欢迎来到「C位」,它是CMC资本团队全新打造的与创业圈、科技产业、学术界分享交流的频道。通过这个窗口,我们关注和记录在当下发生的诸如企业数字化、产业智能化、业务自动化、无人驾驶与智能车、新能源技术、元宇宙等一系列科技领域中的技术前沿、创业实践,以及行业趋势思考,内容形式包括业界对话、行业观察、投资观点等等。我们期望以开放的信息分享和坦诚的观点解构为特色,注重质量,持续输出。

承接上一期内容,本期「C位观察」由CMC资本投资副总裁赵凡执笔,给大家带来AIGC领域主题研究的下篇:AIGC时代的高性能计算基础设施布局新机遇(下)。

赵凡 Fan Zhao

CMC资本 投资副总裁

专注投资领域:先进封装、chiplet、存储、DPU、半导体生产设备及材料、CIM

长文预警:本文约5800字,

预计阅读时长:15分钟

0

引言

在当下中美科技脱钩的背景下,特别是美国芯片法案等一系列政策环环设卡围追堵截中国集成电路行业的发展,当务之急是快速实现自主可控和国产替代。CMC资本半导体基金团队,深刻领会国家在集成电路产业发展的战略布局,集中在新一代人工智能基础设施上深入发掘。集成电路是现代化产业体系的核心枢纽,关系国家安全和中国式现代化进程。我国已形成较完整的集成电路产业链,也涌现了一批优秀企业和企业家,在局部已形成了很强的能力。尤其是我国拥有庞大的芯片消费市场和丰富的应用场景,这是市场经济下最宝贵的资源,是推动集成电路产业发展的战略性优势。CMC资本利用自身团队在chiplet、存储、先进封装等领域的行业积累,发挥产业基金作为懂行业资本的集聚效应,整合行业上下游并加快促进突破卡脖子环节。

1

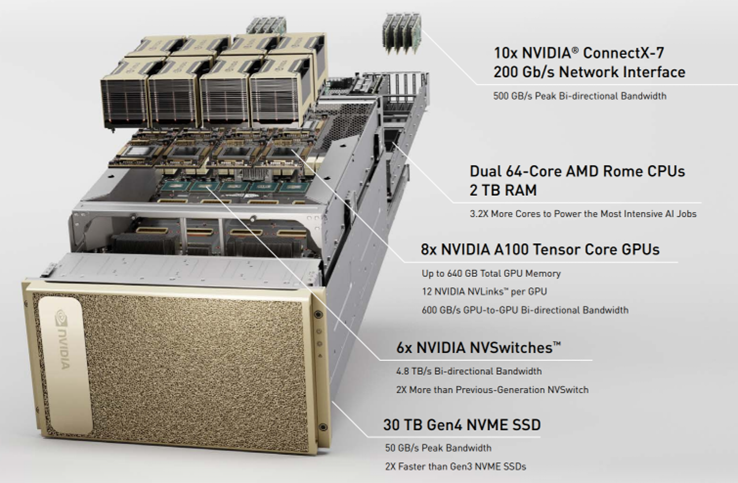

在上一部分《AIGC时代的高性能计算基础设施布局新机遇(上)》(点击回顾上期内容)中,我们着重探讨了大模型时代对算力的需求,引发了以DSA为代表的训练和推理场景芯片的需求;然而,AI数据中心的性能提升并不是仅仅提升算力,而必须要构建出一个算力、存储和网络(所谓三驾马车)平衡的系统,让我们以NVIDIA DGX A100和NVIDIA DGX H100 AI基础架构系统服务器为例,去探究当今具备产品力的服务器的基本架构是如何实现三驾马车的“平衡”的。

图:DGX A100服务器的内部构造

DGX A100/H100在配置上

1)存储和内存配置:

DGX A100搭载双路AMD Rome 7742,共128个核心、基频为2.25 GHz;DGX H100则搭载Intel的Sapphire Rapids Xeon双路 x86 CPU;二者服务器CPU的RAM均是2TB

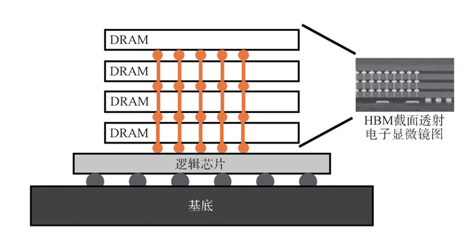

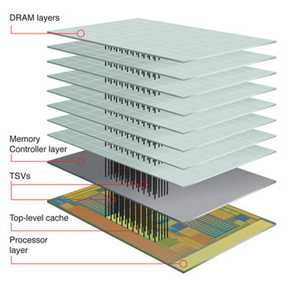

GPU的内存本身搭载了三星/海力士HBM2e产品的A100 80GB GPU,能实现1.94TB/s的峰值带宽,部分H100 GPU型号已搭载HBM3产品。HBM[i](高带宽内存)则是存储领域的核心技术之一,其主要是通过硅通孔(TSV)等技术保证了DRAM的连通效率,并依靠DRAM芯片的堆叠来在单位面积里提升存储密度,形成实现大容量,高位宽的DDR组合阵列。

图:HBM芯片结构示意图

在存储端,DGX A100服务器搭载8个 3.84TB(共计30TB)NVMe SSD硬盘,峰值传输带宽为50GB/s,用来存储非即时运算的AI训练数据;电源部分,DGX A100最大功耗为6.5kW,搭配了6个电源;风扇模组由8 个风扇组成,和传统服务器架构相差不大

2)通信及数据互通:

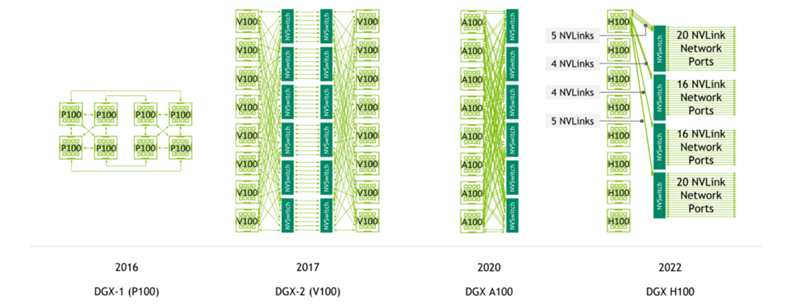

DGX A100搭载了8块NVIDIA A100 80GB Tensor Core GPU,使整个服务器的总显存来到640GB,而DGX H100则是8块H100 GPU,总显存也是640GB。为了真正达成显存扩容的效果,需要在架构上引入新技术,NVIDIA对此的方案是NVLink标准和承载它的模组NVSwitch,它本质上仍是交换机系统。[ii]

图:NVSwitch与DGX各代服务器对GPU互连的方案

DGX A100采用8个单端口ConnectX-7 InfiniBand+2个双端口ConnectX-7 VPI,双向带宽峰值达 500 GB/s;而DGX H100采用8个单端口ConnectX-7 InfiniBand+2个双端口 NVIDIA BlueField-3 DPU VPI

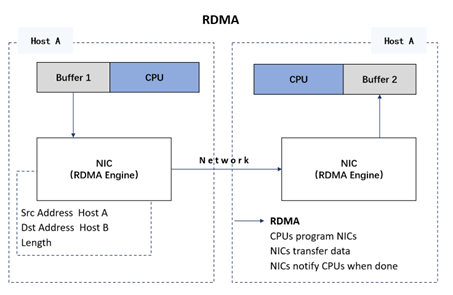

InfiniBand是RDMA(Remote Direct Memory Access)技术的一种协议形式,通过将协议固化在网卡上,能够绕开CPU,实现远程数据的直接存储,从而进一步沟通GPU(8张网卡对应8颗GPU);DPU作用在于承载网络堆栈算法和传输协议运算转移,从而释放CPU的算力资源,助力其他计算模块高效处理业务数据。

纵览DGX A100/H100的架构,不难发现除了常规的CPU、GPU性能提升之外,其他硬件例如HBM等大容量,高带宽DRAM、智能网卡、DPU等,以及协议/架构例如NVSwitch、CXL、RDMA等,都在服务器架构中发挥了重要的作用,也是CMC资本持续关注的技术方向。

2

存储端

一、AI训练数据数量巨大,对存储的容量和带宽、包括新的连接方式和存储架构设计等都提出更高的要求

AI训练数据呈现出海量、非结构化、小文件和读密集型的特点:

海量:大模型的解释力与训练模型的参数量正相关,支撑超大参数的训练需要大量数据;

非结构化:AI训练数据的编码方式、大小、格式以及对应缺失的可能性,都决定了训练数据是非结构化的,在多模态的浪潮中,非结构化的特性会进一步凸显;

小文件:在分布式、多任务训练中,AI训练数据会进一步细分为小文件,以提高训练的独立性和效率,并降低模型过拟合概率;

读密集型:AI模型参数的更新通常是在多个小批量数据的基础上进行的,每个批量数据被处理后,被更新的参数会写回到内存。相对于读操作,这种写操作的频率要低很多。

随着AI训练算力需求不断攀升,底层存储架构的 I/O 数量难以匹配计算性能, GPT3.5的参数量已达1750亿,其原始训练语料大小为45TB,大量的数据需要容量与之匹配且低成本的存储,而并行训练架构使得DRAM的密度、带宽与连接都提出了新的要求。

二、存储技术未来方向

1. 大量热数据存储依赖大容量高带宽DRAM,3D DRAM作为新技术路径可进一步推进目前技术瓶颈

近20年间,运算设备的算力提高了约9万倍,而存储器从 DDR 发展到 GDDR6x,能够用于显卡、游戏终端和高性能运算,接口标准也从 PCIe1.0升级到NVLink3.0,但是通信带宽的增长只有30倍,和算力相比提高幅度非常缓慢,带来“内存墙”问题。同时,为了满足当前AI模型的算力需求,提出了内存的分层架构,将DRAM用于需要高性能访问的热数据,容量层用于不经常访问的冷数据。随着模型逐渐变大,给热数据存储容量也带来了较大的挑战。

制程限制和DRAM存储单元的结构特性决定了其在二维上的缩放已进入瓶颈,传统DRAM的密度(集成度)很难实现明显提升。3D异构DRAM等新结构将成为人工智能时代下的解决大容量、高带宽内存的解决方案之一。[iii]

3D异构DRAM将DRAM array和逻辑芯片用hybrid bonding或其他技术集成在一起,从而提高了DRAM的高度集成和更高的单位面积容量,并通过数千个(甚至更多)TSV连通上下芯片来提供超高的数据传输带宽,各大存储厂商都在积极布局3D DRAM技术,如三星、SK海力士等,并视其为技术趋势。利用3D异构DRAM结构可以使用成熟制程做出接近先进制程密度与带宽的存储芯片,是符合当下国情的技术发展趋势,目前,国内已经开始涌现有一定技术能力的3D DRAM公司。

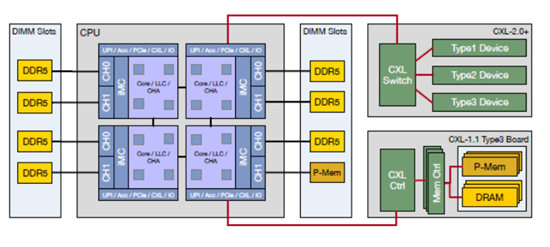

2. CXL 架构下弹性扩充DRAM容量

由于内存通道的增加会提升CPU的计算成本和功耗,在CPU核数量不断增长的同时,其内存通道数增速缓慢,每个CPU核所拥有的内存通道持续下降,无法发挥最大性能。[iv]

CXL基于PCIe物理层的基础上构建缓存一致性系统,同时提供了数倍于PCIe的数据传输速度。CXL1.0能够实现多个计算单元(例如GPU)与CPU内存之间的直接访问,例如在AI加速器(常见有专门化的GPU、FPGA等)可通过CXL1.0和CPU直连,从而提升AI训练和推理效率。

CXL 2.0 和 3.0 在“按需”的基础上为主机分配内存,从而提供更高的内存利用率和效率。CXL2.0构建了交换和池机制,以建立更好的设备内存互访系统,使得内存扩展和内存共享机制成为现实;云计算强调计算资源的可获取性和灵活度,于去年所发布的CXL3.0则进一步强调了这个概念,其不仅可以在一个机柜里实现计算存储资源的池化与耦合,而且可以在多机柜间建立更大的资源池。[v]

AMD 和Intel分别推出了Genoa、Meteor Lake两款CPU芯片,均支持CXL3.0,旨在将CPU连接到多个I/O设备。未来,CXL协议有望使得CPU与内存的配比更灵活,甚至实现近端内存的完全取消和远端内存的持久化,届时,计算中心的计算和内存资源将会得到最充分的利用和配合。

3

网络端

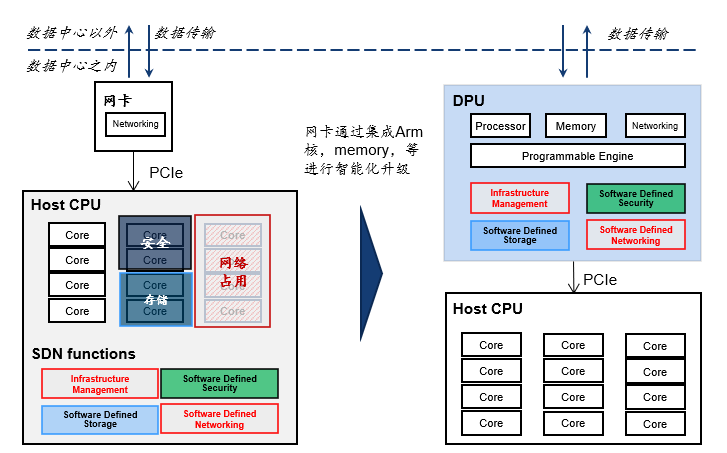

一、DPU的核心效用在于释放CPU算力资源、助力其他计算模块高效处理业务数据,然而国内DPU下游需求不确定性较高,DPU落地还面临挑战

2020 年,英伟达在 GTC 战略发布中将 DPU 定义为“第三颗主力芯片”,行业自此进入蓬勃发展期。DPU是基于数据中心生态中,作用在于承载网络堆栈算法和传输协议,从其实际经济效益目标来看,主要分为降本和增效两部分:

• 降本:体现在数据面卸载和虚拟化场景支持两方面

• 增效:主要体现在HPC/AI中对于高速与频繁I/0访问,对内存频繁读写场景的需求

2022年是DPU爆发的元年,国内涌现了一批对标BlueField-2/3 DPU的初创公司,CMC资本也同步系统性地分析DPU行业并梳理了国内DPU厂商,认为海外头部DPU公司在技术路线和应用场景非常明确,但国外大厂(英伟达、英特尔、Pensando)的方案不一定能够完全满足国内本土的需求,且多数公司已被大厂收购。国内厂商面临的挑战在于:1)难以做出完全对标BlueField-2/3 DPU;2)下游客户需求高度不确定,面临高度客制化开发导致经营困难,抑或是难以开发通用型DPU。因此国内初创企业要贴近客户需求并抓住中国互联网环境特性,方便落地的弹性解决方案是更好适应目前中国的DPU市场路径。

二、基于RDMA协议并提供数据面卸载的SmartNIC将为云厂商自定义的云基础设施赋能

中国东数西算工程按照全国一体化大数据中心体系布局,8个国家算力枢纽节点将作为我国算力网络的骨干连接点,发展数据中心集群,开展数据中心与网络、云计算、大数据之间的协同建设,旨在将对网络要求不高的计算任务引导到西部数据中心。然而,人工智能推理等对网络时延要求较高的任务依然无法部署在西部,大规模算力网络集群通信场景下,支持集群内异构服务器网卡互访互通是亟需解决的重要问题。

RNIC (RDMA Smart NIC)可以将 vSwitch 完全offload,释放昂贵的 Host CPU 资源;实现基于服务器的复杂网络数据平面功能,例如:多匹配操作处理、计量整形、流统计等;并且支持网络的可编程性(通过更新的固件或客户编程),与现有的开源生态系统无缝协作,以最大程度地提高软件功能的速度和影响力。通过将RDMA协议固化于网卡(NIC)上,可实现远程数据的直接存储,让主机间的数据传输能绕过操作系统和CPU,具有零拷贝、低延迟、高吞吐量的特点。

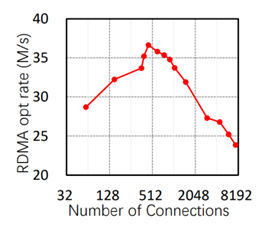

一方面,RDMA的连接状态必须存储在RDMA网卡(RNIC)上,而网卡的性能限制,导致了RDMA并发能力有限,当RNIC需要维持大量并发连接的时候,性能会明显下降。如图,目前性能最强的RNIC,其峰值性能只能支持约450个并发连接,随后会有明显的性能衰竭。这导致RDMA实际上难以支持大规模节点的连接。[vi]

在大模型训练中,GPU集群规模越大,总算力固然会提升,但是每块GPU实现的平均算力会逐渐下降,RDMA的有限并发能力是其原因之一。更棘手的是,当通讯发生拥堵(congestion),网卡被迫降速解决传输问题,可能会造成模型训练的中断和延迟。GPT3.5已经高达1750亿个参数,当高并发的问题能够解决,大模型参数量仍有广阔的扩展空间;另一方面,当GPU集群的总算力和平均算力能够得到提升,且损耗降低,高频更新(甚至实时更新)的大模型或许能够成为现实。

综上所述,2023年无疑是AIGC的元年,点燃了在算力、存储、通信等整体架构和基建上的持续投入和演变。我们也将加大在关键技术路径的探索,结合基金自身的产业及政府资源,帮助行业加速发展,突破关键技术节点,早日实现国产替代和弯道超车。

参考资料:

[i] Jun H, Nam S, Jin H, et al. High-bandwidth memory (HBM) test challenges and solutions[J]. IEEE Design & Test, 2017, 34(1): 16-25

[ii] https://developer.nvidia.com/zh-cn/blog/upgrading-multi-gpu-interconnectivity-with-the-third-generation-nvidia-nvswitch/

[iii] 来源:Techradar (https://www.techradar.com/news/computing-components/3d-processors-memory-and-storage-explained-987509)

[iv] 来源:了不起的云计算 (https://www.sohu.com/a/647391149_711053)

[v] 来源:CXL官网 (https://www.computeexpresslink.org/about-cxl)

[vi] 来源:IEEE ICNP (https://icnp21.cs.ucr.edu/papers/icnp21camera-paper30.pdf)